Présentation

Auteur(s)

-

Thomas SKOTNICKI : Docteur en microélectronique - Ingénieur de recherche à France Télécom - Centre national d’études des télécommunications (CNET) de Grenoble - Ingénieur ST Microelectronics

Lire cet article issu d'une ressource documentaire complète, actualisée et validée par des comités scientifiques.

Lire l’articleINTRODUCTION

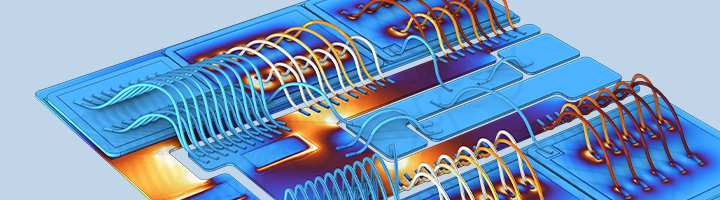

Le transistor MOS est, de loin, le dispositif le plus répandu dans la production actuelle de composants semi-conducteurs, car il est le composant de base de la technologie CMOS (Complementary MOS), qui, à elle seule, englobe plus de 70 % de la production mondiale de circuits intégrés.

Plusieurs sigles plus ou moins justifiés sont utilisés dans la littérature pour décrire le transistor MOS (Metal Oxide Semiconductor) : MOSFET (MOS Field Effect Transistor), IGFET (Insulated Gate Field Effect Transistor) et MOST (Metal Oxide Semiconductor Transistor).

Le transistor MOSFET se caractérise par le fait que la grille, par l’effet de champ électrique, contrôle à travers l’oxyde de grille la densité de porteurs dans le canal du dispositif et ainsi l’intensité du courant dans le canal. Le canal est relié de part et d’autre à deux régions fortement dopées entre lesquelles est appliquée une tension donnant lieu à la circulation du courant. Ce transistor n’est qu’un élément d’une famille plus vaste de composants dits FET (Field Effect Transistor) utilisant l’effet de champ pour moduler l’intensité du courant dans un canal. En fait, on distingue trois groupes dans la famille des FET :

-

le IGFET, dont l’effet de champ provient d’une grille isolée du canal par un diélectrique mince ; actuellement, le diélectrique utilisé presque exclusivement, est l’oxyde SiO2 d’où la dénomination MOSFET ; cependant il faut remarquer que d’autres diélectriques, comme Si3N4, un empilement SiO2/Si3N4 ou un empilement SiO2/Ta2O5, peuvent aussi être utilisés ;

-

le JFET (Junction FET), dont l’effet de champ provient d’une jonction PN polarisée en inverse ; si la région P est la grille, elle module l’épaisseur du canal (région N) et, ainsi, son courant par l’extension de la zone de charge d’espace sous l’effet de la polarisation inverse de la jonction ;

-

le MESFET (Metal Semiconductor FET), dont l’effet de champ provient d’une jonction Schottky (métal-semi-conducteur) polarisée en inverse, le fonctionnement de la grille métallique étant analogue à celui de la grille du JFET.

Dans cet article concernant le transistor MOS (IGFET ou MOSFET), nous aborderons son fonctionnement ainsi que la technologie de fabrication. Le fonctionnement est décrit suivant trois niveaux de difficulté :

-

un niveau qualitatif, permettant d’acquérir une bonne intuition du principe de fonctionnement du transistor ;

-

un niveau « modèle simplifié », permettant de décrire le fonctionnement d’un transistor idéal ;

-

un niveau « modèle complet », permettant de comprendre tous les effets parasites, ainsi que ceux dits secondaires, et d’analyser leur impact sur les caractéristiques du transistor.

La partie technologique montre l’intérêt de tous les éléments de l’architecture du transistor et de leurs modes de réalisation technologique. Différentes architectures de transistors (par exemple, à canal surfacique, à canal enterré, à canal à hétérostructure, etc.) sont détaillées, ainsi que l’assemblage d’une technologie complète.

Le fonctionnement et l’architecture des principaux types de circuits CMOS logiques, ainsi que les problèmes relatifs à l’intégration des circuits sur une puce de silicium sont présentés dans l’article Circuits intégrés CMOS sur silicium

Voir en fin d’article les tableaux Abréviations et Notations et symboles.

VERSIONS

- Version archivée 1 de sept. 1987 par René MICOLET

DOI (Digital Object Identifier)

Présentation

Article inclus dans l'offre

Actualisée et enrichie d’articles validés par nos comités scientifiques.

Quiz, médias, tableaux, formules, vidéos, etc.

Opérationnels et didactiques, pour garantir l'acquisition des compétences transverses.

Un ensemble de services exclusifs en complément des ressources.

3. Effets correcteurs

Le fonctionnement d’un transistor long et large (W ; L > > 1 µm) est correctement décrit par le modèle présenté dans le paragraphe 2.

Le transistor submicronique subit l’influence de plusieurs effets correcteurs, parasites, dont les manifestations peuvent être considérées comme étant de second ordre lorsque

µm. Pourtant, pour des transistors profondément submicroniques (W ; L << 1 µm), ces effets peuvent dominer complètement le fonctionnement du dispositif et le rendre inutilisable. Pour cela, il est important de comprendre et de modéliser les effets correcteurs, afin d’être capable de concevoir l’architecture du transistor de manière à minimiser leur impact. Une génération technologique est considérée viable pour l’industrialisation lorsque le comportement du transistor nominal, pour cette technologie, ne s’éloigne pas trop du comportement type du transistor long et large. D’une manière quantitative, l’intensité maximale tolérable d’un effet parasite donné est définie dans les documents dits spécifications électriques de la technologie.

µm. Pourtant, pour des transistors profondément submicroniques (W ; L << 1 µm), ces effets peuvent dominer complètement le fonctionnement du dispositif et le rendre inutilisable. Pour cela, il est important de comprendre et de modéliser les effets correcteurs, afin d’être capable de concevoir l’architecture du transistor de manière à minimiser leur impact. Une génération technologique est considérée viable pour l’industrialisation lorsque le comportement du transistor nominal, pour cette technologie, ne s’éloigne pas trop du comportement type du transistor long et large. D’une manière quantitative, l’intensité maximale tolérable d’un effet parasite donné est définie dans les documents dits spécifications électriques de la technologie.

3.1 Régime de conduction

Plusieurs effets viennent perturber la caractéristique idéale du TMOS en régime de conduction. Avant de les analyser un par un, regardons de manière globale et simplifiée leurs impacts sur la caractéristique de sortie.

La figure 13 fait le bilan des effets correcteurs influençant la caractéristique de sortie IDS – VDS du TMOS :

Certains effets tels que le DIBL et le perçage, même s’ils laissent leurs empreintes sur les...

Effets correcteurs

Article inclus dans l'offre

Actualisée et enrichie d’articles validés par nos comités scientifiques.

Quiz, médias, tableaux, formules, vidéos, etc.

Opérationnels et didactiques, pour garantir l'acquisition des compétences transverses.

Un ensemble de services exclusifs en complément des ressources.

BIBLIOGRAPHIE

-

(1) - CAND (M.), DEMOULIN (J.-L.), LARDY, SENN (P.) - Conception des circuits intégrés MOS, - Éditions Eyrolles et CNET-ENST, 1986.

-

(2) - ARRORA (N.) - MOSFET Models for VLSI Circuit Simulation. - Springer Verlag 1993.

-

(3) - COLINGE (J.-P.), VAN DE WIELE (F.) - Physique des dispositifs semi-conducteurs. - De Bœck-Wesmael, 1996.

-

(4) - SZE (S.-M.) - Physics of semiconductor devices, - J. Wiley & Sons, 1981.

-

(5) - GROVE (A.-S.) - Physics and technology of semiconductor devices, - J. Wiley & Sons, 1967.

-

(6) - SKOTNICKI (T.), MERCKEL (G.), PEDRON (T.) - A new punchthrough current model based on the Voltage-Doping Transformation. - IEEE Transaction on Electron Devices, pp. 1076-1086, July 1988.

-

...

Article inclus dans l'offre

Actualisée et enrichie d’articles validés par nos comités scientifiques.

Quiz, médias, tableaux, formules, vidéos, etc.

Opérationnels et didactiques, pour garantir l'acquisition des compétences transverses.

Un ensemble de services exclusifs en complément des ressources.