Conçu par Soitec, le substrat FD-SOI améliore l'efficacité énergétique des transistors sans alourdir les coûts de production. Ces qualités sont prisées par la filière de microélectronique basse consommation.

L’Internet des objets prépare des lendemains qui chantent pour l’industrie de la microélectronique, dont les recettes sont déjà florissantes : un peu plus de 400 milliards de dollars cette année (contre 300 milliards en 2010) selon Gartner, les ventes mondiales de semi-conducteurs ayant progressé de 16,8%. Mais ces objets pour la plupart autonomes requièrent des micro-composants électroniques qui ne dévorent pas leur batterie avec gloutonnerie. Dans cette course à la sobriété énergétique, le procédé FD-SOI (Fully Depleted Silicon on Insulator), mis au point par la société iséroise Soitec (issue du CEA-LETI) avec le concours de STMicroelectronics, améliore l’architecture même du transistor, ce composant fondamental des puces et des circuits électroniques intégrés.

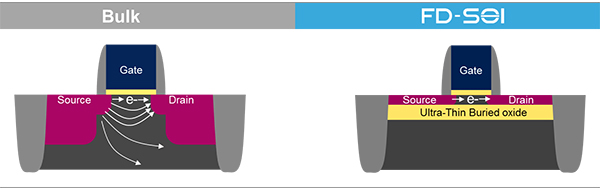

Le FD-SOI a pour objectif de réduire voire d’annuler les courants de fuite parasites, dont l’importance grandit à mesure que la miniaturisation des transistors progresse : des électrons se «perdent» en chemin entre la source et le drain du transistor. Or, ces courants de fuite dégradent le rendement et provoquent des comportements aléatoires. « Un transistor peut être comparé à un robinet à électrons qui, lorsqu’il est très petit, fuit en permanence et ne permet plus de distinguer un état ouvert d’un état fermé, explique Manuel Sellier, responsable marketing produits chez Soitec. Tant que la finesse de gravure ne descendait pas sous les 130 nanomètres, les phases de fabrication étaient assez simples à mettre en œuvre. En dessous et jusqu’à 28 nm, l’évolution n’a été envisageable qu’au prix de percées technologiques majeures, comme le remplacement de l’aluminium par le cuivre pour réaliser les interconnexions. A partir de 28 nm, l’architecture du transistor devait être modifiée. »

Un isolant confine les électrons

C’est la raison d’être du procédé FD-SOI, qui s’applique aux tranches de silicium (wafer) fournies par les fabricants de silicium, placés en amont de la filière. C’est un moyen de « raffiner » cette matière première et de la transformer en un substrat sur lequel les fondeurs graveront plus tard les transistors. La technique consiste à superposer, sur le matériau brut en silicium, une couche d’oxyde amorphe de 20-25 nm d’épaisseur puis une autre couche de silicium de 6 nm d’épaisseur, où sont implémentés les canaux du transistor. La couche d’oxyde agit comme un isolant et confine les électrons entre la source et le drain. « D’autre part, le remède classique contre les courants de fuite, qui impose toujours plus de dopants, n’est plus nécessaire » poursuit Manuel Sellier. Si le principe du silicium sur isolant n’est pas nouveau, l’uniformité des couches et la jonction entre les matériaux cristallins et amorphes ont été perfectionnées grâce à la méthode de fabrication Smart Cut du CEA-LETI, précise à l’atome près.

La technologie FinFET (Fin Field Effect Transistor) est une alternative qui limite également les courants de fuite. Elle intervient pendant la phase de gravure et permet de créer des transistors à ailette en 3D. Mais elle est moins compétitive, selon Manuel Sellier : « le FD-SOI reste une solution planaire, moins complexe à maîtriser pour nos clients, c’est-à-dire les fondeurs. » Du reste, les finalités ne sont pas tout à fait les mêmes. « La performance a été le premier critère de choix qui a guidé le développement du FinFET, observe Manuel Sellier. Les puces FinFET se destinent aux serveurs informatiques, aux PC… Avec le FD-SOI, nous avons cherché le meilleur compromis entre consommation énergétique, performance, densité et coût, afin d’adresser le marché de la basse consommation. »

STMicroelectronics, Samsung et GlobalFoundries sont les trois fonderies qui ont adopté le FD-SOI et proposent des circuits gravés en 28, 22 et bientôt 18 nm, avec le 12 nm en perspective. Le FinFET fait d’ores-et-déjà mieux (10 nm) mais la majorité du marché se concentre encore sur la production en 28 nm. Les premiers produits finaux bénéficiant de circuits FD-SOI font leur entrée sur le marché depuis deux ans environ. Une « smartwatch » de Sony démontre l’intérêt de cette technologie. « Le circuit GPS réalisé à partir d’un substrat FD-SOI consomme cinq fois moins et permet d’obtenir une autonomie de 35 heures, GPS activé » confie Manuel Sellier. L’automobile, en particulier les véhicules autonomes, et les radiocommunications sont d’autres débouchés potentiels. Soitec a l’ambition de porter l’étendard du « made in France » au milieu des géants américains et asiatiques.

Frédéric Monflier

Réagissez à cet article

Vous avez déjà un compte ? Connectez-vous et retrouvez plus tard tous vos commentaires dans votre espace personnel.

Inscrivez-vous !

Vous n'avez pas encore de compte ?

CRÉER UN COMPTE